Stručná historie firmy Cyrix:

1988 - několik inženýrů z Texas Instruments založilo vlastní firmu Cyrix, která byla zpočátku zaměřena na návrh alternativních FPU pro 286 a 386, později CPU 486SLC/DLC/SX/SX, 5x86, 6x86.

1997 - Cyrix byl koupen firmou National Semiconductor, zaměření přešlo na integrované CPU + video + audio - čip MediaGX.

1999 - Po neúspěchu CPU Cyrix MII odkoupil Cyrix taiwanský výrobce čipsetů VIA. V tomtéž roce VIA koupila malou firmu Centaur od IDT, která navrhovala CPU WinChip a Centaur x86.

2000 - VIA vydala CPU Cyrix III založený na jádru Joshua, které dříve vyvíjel Cyrix (pozdější varianta však byla založená na jádře Samuel týmu Centaur).

2001 (Q1) - VIA vydala CPU Cyrix III 733 MHz s novým jádrem Samuel 2 (přidána L2 cache 64 kB).

2001 (Q3) - VIA vydala CPU C3 800 MHz s novým jádrem Samuel 3 AKA Ezra vyrobený 0,15um technologií.

2002 (Q1) - VIA vydala CPU Mobile C3 933 MHz (jádro Ezra-T) vyrobený 0,13um technologií.

2003 (Q1) - VIA vydala CPU C3/Eden 1,2 GHz s novým jádrem Nehemiah vyrobený 0,13um technologií.

2003 (Q2) - VIA vydala CPU Mobile C3/Antaur 1,2 GHz (jádro Nehemiah) vyrobený 0,13um technologií.

Přehled rodiny VIA C3:

| typ | fcore [MHz] | FSB [MHz] | fFPU | L1/L2 [kB] | tech. [um] | Vcore [V] | Pmax [W] | socket | instr. sady |

| Cyrix MII | 225-300 | 66-100 | 1:1 | 64/- | 0,25/0,18 | 2,9/2,2 | 28 | S-7 | MMX |

| Cyrix III (Joshua) | 333-450 | 66/100/133 | ? | 64/256 | 0,18 | 2,2 | 25 | S-370 | MMX, 3DNow! |

| Cyrix III (Samuel) | 500-733 | 66/100/133 | 1:2 | 128/- | 0,18 | 1,9/2,0 | 19 | S-370 | MMX, 3DNow! |

| Cyrix III (Samuel 2) | 650-800 | 66/100/133 | 1:2 | 128/64 | 0,15 | 1,5/1,6 | 12 | S-370 | MMX, 3DNow! |

| C3 (Ezra) | 800-1000 | 66/100/133 | 1:2 | 128/64 | 0,15/0,13 | 1,35 | 10 | S-370 | MMX, 3DNow! |

| C3-M (Ezra-T) | 900-1200 | 66/100/133 | 1:2 | 128/64 | 0,13 | 1,35 | 10 | S-370 | MMX, 3DNow! |

| C3 (Nehemiah) | 1000-1400 | 66/100/133 | 1:1 | 128/64 | 0,13 | 1,4 | 19 | S-370 | MMX, SSE |

| C3-M (Nehemiah) | 1000-1400 | 66/100/133 | 1:1 | 128/64 | 0,13 | 0,8/1,25 | 7/15 | S-370 | MMX,3DNow!,SSE |

| C4 (Esther) | 1000-2000 | až 800 | 1:1 | 128/>64 | 0,09 | ? | 3,5 @1G | ? | MMX, SSE1-3 |

VIA C3 (Nehemiah):

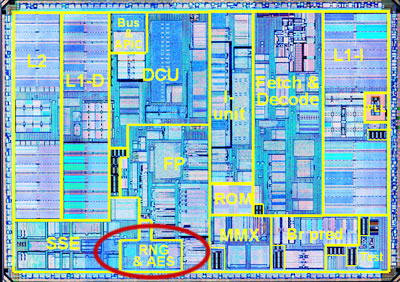

foto jádra Nehemiah 52 mm2

vnitřní blokové schema jádra Ezra

Řada VIA C3 založená na jádře Nehemiah se standardně vyrábí pro frekvence jádra 1000, 1130, 1200, 1300 a 1400 MHz a systémové sběrnice 133 MHz (umožňuje pracovat i při 66 nebo 100 MHz - nastaví se piny BSEL0, BSEL1). Násobič není uzamčen natvrdo, ale lze ho softwarově změnit zápisem do příslušného MSR registru v rozsahu 3,0 až 16,0 po 0,5 (5 bitů).

CPU je kompatabilní s procesory intel, liší se pouze v některých drobnostech jako monitorovací a debugovací funkce, MSR, rozšíření CPUID instrukce (vrací mj. přímo ASCII řetězec s názvem CPU), a přidává některé nové funkce. Za zmínku stojí technologie PadLock, která v sobě zahrnuje 2 generátory náhodných čísel a instrukce pro AES šifrování. hardwarový generátor náhodných čísel pro podporu šifrování AES. Naopak některé funkce chybí, jako např. 36-bit rozšířené adresování a 2MB stránky, což ale na desktopech (kde se nepředpokládá více jak 4 GB RAM) nevadí. Starší verze nepodporovaly APIC (Advanced Peripheral Interrupt Controller) a multiprocessing. Pinově je kompatabilní s PGA370 procesory od intelu vyjma některých rezervovaných pinů, které se používají např. pro JTAG/TAP boundary scan.

Procesor je vybaven dynamickým řízením spotřeby, které za běhu odpojuje jednotlivé části jádra, které nejsou právě potřeba. Je definováno 5 Power Management režimů:

Rozsahy pracovních teplot jsou 0-70°C pro CPGA pouzdro a 0-85°C pro EBGA pouzdro. Teplotu jádra lze snímat pomocí vnitřní diody vyvedené na piny THERMDN a THERMDP.

Na jádře Nehemiah byly postaveny další procesory, které VIA pojmenovala Eden (N, ESP) a Antaur (tedy spíše přejmenovala z původního C3, přičemž odpadl údaj o frekvenci). Procesory Eden mají ještě více sníženou spotřebu na max. 7W @1GHz (pasivní chlazení) při sníženém napájecím napětí 0,8-1V. Zatímco Eden-ESP je ve standardním pouzdru EBGA, tak Eden-N byl zmenšen na pouhých 15 x 15 mm do pouzdra Nano-BGA.

| typ | Pmax [W] |

| VIA Eden-N 1 GHz | 7 |

| VIA Eden ESP 1 GHz | 7 |

| VIA C3-M 1 GHz | 11 |

| VIA C3 1 GHz | 15 |

| AMD Mobile Athlon 4 1,1 GHz | 25 |

| intel Pentium IIIs 1,13 GHz - | 29 |

| intel Celeron 800 MHz | 21 |

Porovnání výkonu:

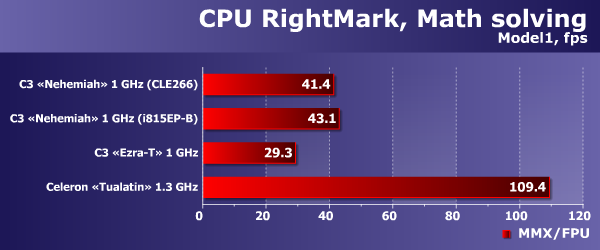

test řešení diferenciálních rovnic využívající x87 a MMX instrukce

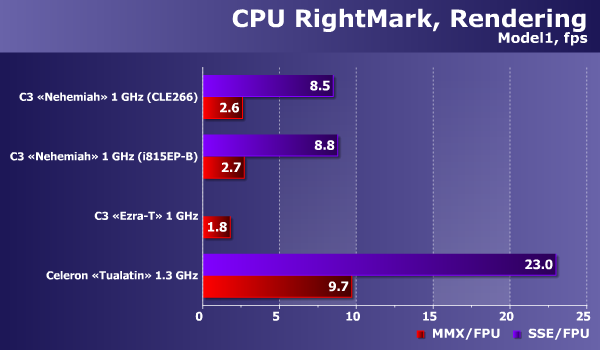

test renderingu s využitím SSE a bez

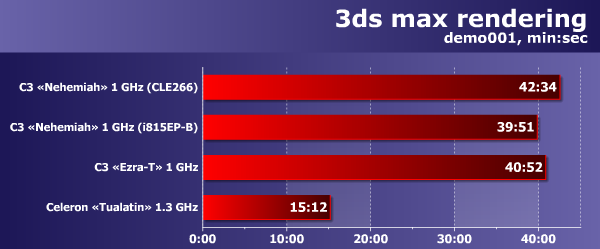

rendering reálné scény v 3D Studiu MAX

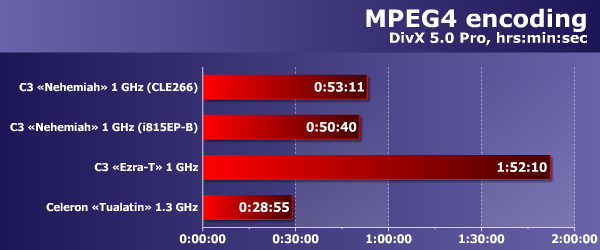

kódování MPEG-4 videa

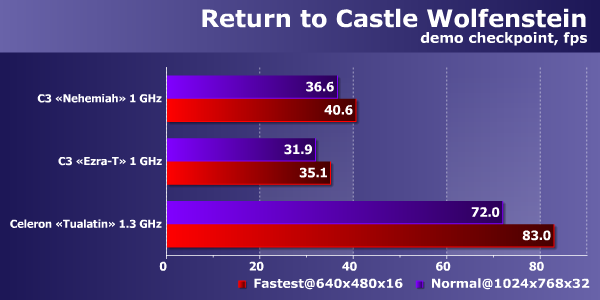

timedemo ve hře Return to Castle Wolfenstein (OpenGL)

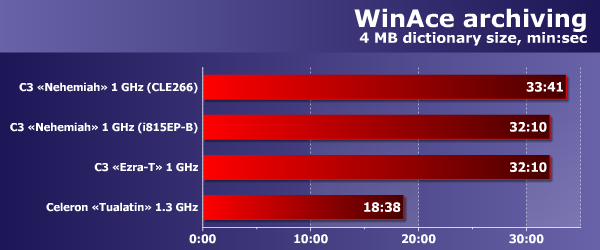

komprese souborů pakovačem WinACE (závisí dost na propustnosti pamětí)

budoucí CPU VIA C4 (Esther)

bude pro VIA vyrábět firma IBM 90nm SOI technologií. Očekávaná spotřeba 1GHz verze by měla být 3,5 W. Zvětší se L2 chache, zrychlí FSB až na 800 MHz (efektivně, QDR) a přibudou instrukce SSE2 a SSE3. V procesoru bude zabudovaná jednotka pro RSA šifrování a NX atributy pro nastavení oblasti paměti, ze které nebude možno spustit kód (podpora v Windows XP SP2) pro zvýšení stability.

FPU init hack - zrychlení práce s FPU jednotkou

FPU procesorů VIA C3 (se starším jádrem Samuel) je pomalý mimo jiné díky ne úplně dobře dotažené architektuře pipeliningu, kdy při generování výjimky dochází k velkým časový ztrátám. Kompilátory inicializují FPU zhruba takto (Borland Delphi 7.0):

fninit wait fldcw word $1372 retkdy se povolují výjimky dělení nulou, přetečení, atp. Pokud necháme maskované všechny výjimky, lze dosáhnout zrychlení o 50-150%. Stačí tedy inicializaci upravit na:

fninit wait retO obsluhu výjimek se pak ale musíme v programu starat sami načítáním stavového slova FPU nebo vhodnou kontrolou ještě před výpočtem v FPU.

Odkazy:

http://www.computerbase.de/lexikon/VIA_C3

http://users.erols.com/chare/elec.htm

http://www.vanshardware.com/articles/2004/03/040331_C3Fpu/040331_C3Fpu.htm

http://www.digit-life.com/articles2/roundupmobo/via-c3-nehemiah.html http://www.cpushack.net/VIA.html

a další -> http://www.google.com