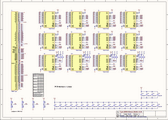

S ohledem na cenu (neboť SIMM modul překračuje svou délkou limit 10 cm u JLCPCB) jsem se rozhodl pro 2-vrstvý layout, který není úplně optimální z hlediska signálové integrity a tak jsem alespoň nešetřil blokovacíma kondíkama pro každý DRAM čip. ID bity jsem připojil na konfigurační odpory, aby bylo možné flexibilně nastavit kapacitu a rychlost modulu, viz tabulka ve schematu. Plošňáky jsem nechal vyrobit u JLCPCB v rámci větší várky (5 ks mě stálo 5,5 $), dorazily minulé úterý. Destičku jsem nejprve osadil jen 8 DRAM čipy, které jsem vypájel z 16MB FPM 60ns modulu, jenž jsem sehnal za 50 Kč na poslední strašnické radioburze. Modul jsem otestoval v základní desce 486 VLB, kde není nutné osazovat více modulů do páru. Asi po hodině prošel Memtest bez chyby.

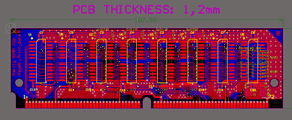

Bohužel při strkání modulu do SIMM slotu nastal dost nepříjemný Fffuuu! moment, kdy jsem zjistil, že jsem modul vyrobil na příliš tlustém FR4 substrátu. Při zadávání desek do výroby jsem si vůbec neuvědomil, že SIMM moduly mají plošňák silný jen 1,2 mm a nikoliv 1,6 mm, což je standardní výchozí hodnota u JLCPCB. Modul sice do slotu nacpat jde, ale záleží na konkrétním slotu, některé mají větší vůli než jiné a nerad bych jim úplně vymačkal kontaktní pérka. Takže plošňáky budu muset vyrobit znovu a přepájet to. Vtipné na tom je, že stejnou chybu udělal i Alexandru Groza na svém 30-pinovém SIMMu, který také musel nechat vyrobit znovu. Na jeho článek jsem narazil už dříve a měl ho uložený, že si ho někdy přečtu off-line, ale nebyl čas.

Abych ověřil kompletní funkci svého modulu, potřeboval jsem sehnat ještě další 4 DRAM čipy. Prohledal jsem šuplíkové zásoby, ale bohužel jsem měl v téhle kapacitě jen EDO SIMMky, které nejdou ve starších kompech použít. Musel jsem tak opatrně odpájet čipy z jiného paritního modulu a přepájet je sem. Modul jsem pak otestoval ve čtveřici v Alpha PC64 a normálně naběhla, takže jiná chyba by tam být neměla...

|

|

|

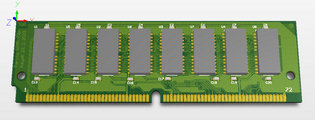

| SIMM 72-pin schema | SIMM 72-pin layout | SIMM 72-pin PCB 3D model |

|

|

| osazený SIMM 72-pin PCB top | osazený SIMM 72-pin PCB bottom |

17.3.2023 Z JLCPCB mi přišla další sada plošňáků na mé paritní SIMM moduly, nyní již ve správné tloušťce 1,2 mm, takže padnou do slotů jako ulité. Chtěl bych poděkovat Jožkovi z OldCompu za poskytnutí 6 FPM 60ns SIMMek na čipy. Bohužel zrovna jeden 16MB paritní modul s čipy LGS vykazoval chybu 2 bitů (v 1 čipu), takže ho nemohu rovnou použít a nemám už další samostatné čipy na opravu, jedině z jiných modulů. Osadil jsem tedy 2 své nové 16MB moduly a k nim přidal další 2 stávající paritní 16MB moduly a zkompletoval tak další čtveřici 16MB modulů, celkem mám nyní osazeno 128 MB paměti.

|

|

|

| SIMMy na čipy | GoldMemory test fail | osazené SIMMy 72-pin v1.1 |

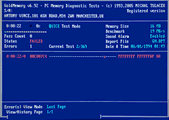

30.3.2023 Od Pwrampa z OldCompu jsem získal 1 obyčejný 16MB FPM 60ns SIMM s čipy Panasonic MN4117400ASJ-06, takže jsem se mohl pustit do opravy paritního SIMMu s čipy LGS GM71C17400BJ60 od Jožky. Dle výpisu chyby z GoldMemory je zřejmé, že jde o bit č. 5, tak jsem propípnul kam vede signál D5 a byl to 3. čip zleva. Odpájel jsem ho foukačkou, nahradil čipem Panasonic a test prošel bez chyby. Když jsem ale modul strčil do Alpha PC64, tak nenaběhl (skončil POST kódem 19h, stejně jako když modul chybí). Domníval jsem se, že by chyba mohla být v některém z paritních čipů, které se v běžném PC netestujou. Postupně jsem tedy vždy jeden čip LGS sfouknul, připájel místo něj čip Panasonic a otestoval. Ale ani po výměně všech 4 paritních čipů systém nenaběhnul - nechápu, asi nějaká jiná nekompatabilita v zapojení modulu (PD bity byly OK, ale jiný modul fungoval i bez nich). Takže jsem nakonec z modulu všechny čipy sfouknul a přepájel je na svůj plošňák.

K mému překvapení však nový modul také nefungoval, ani v Alpha PC64 ani v testovací 486 desce. Proměřil jsem ho na zkraty/přerušení a nic jsem nenašel. Postupně jsem horních 8 čipů LGS vyměnil za Panasonicy, ke kterým jsem měl větší důvěru a modul konečně začal fungovat. Pak jsem zas 1 čip Panasonic odpájel a postupně na jeho pozici připajoval a odpajoval čipy LGS. K mému překvapení bylo 14 z 15 čipů vadných tak, že ve většině případů deska s modulem ani nePOSTla. Asi ve 3 případech nabootovala, ale v Memtestu hned vyběhly chyby a pouze jediný čip LGS prošel Memtestem OK. Modul tedy zůstal nedoosazený, jen jako neparitní. Domnívám se, že čipy LGS už byly nějaké načaté a dodělal jsem je vysokou teplotou při odpajování foukačkou (nastaveno 330°C). Inu, zajímavá zkušenost, jen poněkud časově náročná...

Jak použít EDO RAM čipy FPM RAM

16.5.2023 Narazil jsem na zajímavé video od uživatele Bits und Bolts, kde vysvětluje, jak lze jednoduchou HW úpravou změnit časování čipů EDO DRAM na FPM, což následně demonstruje na své 386 MB osazené novými moduly s 32 MB EDO DRAM (prošly i MemTestem). Nejde přitom o žádnou novinku, uživatel Arti9m vzpomíná, že na to narazil někdy v roce 2005. Fígl je jednoduchý, stačí u každého paměťového EDO čipu odpojit pin OE# od země a připojit ho na sousední pin CAS#, čímž se zkrátí doba výstupu dat na sběrnici tak, jako je u FPM čipu. Takovou úpravu lze jednoduše provést i na stávajícím osazeném modulu. Potenciálně by mohlo působit problém to, že výstup budiče signálu CAS# z řadiče paměti bude kapacitně zatížen 2-násobnou kapacitou (2 vstupy na straně DRAM čipu místo 1), což by při rychlém časování mohlo způsobit zpoždění nad limit. Konkrétně v případě 16MB paritního FPM modulu s 12 čipy visí na 1 CASu 3 vstupy a po úpravě na EDO to bude 6 vstupů na 1 CAS. To by mělo být stejné jako v případě oboustranného 32MB modulu s 24 čipy, který by měl paměťový řadič také zvládnout.Tak mi to nedalo a vzal jsem jeden neosazený plošňák mého SIMM modulu, plošky OE# (22) jsem přelepil proužky nastříhané kaptonové pásky, připájel 8 EDO DRAM čipů Fujitsu MB8117405A-60 z běžného 16MB EDO modulu a nožky OE# (22) a CAS# (23) spojil cínovou kapkou. Modul jsem otestoval v základní desce 486 s chipsetem SiS 85C471 a naběhla bez problémů. V SETUPu jsem nastavil nejrychlejší časování (Write Cycle: 0 W/S, CAS Write Pulse: 1T) a právě doběhl test GoldMemory s 0 chybami, takže to funguje. Tímto se tedy otevírá cesta k výrobě paměťových modulů pro stará PC s využitím běžnějších EDO DRAM čipů.

Oprava vadného 32MB 72-pin SIMMu

5.8.2022 Na pražském blešáku U Elektry se mi podařilo koupit paměťový kit SIMM 72-pin Kingston KTH-VL4/64 2 x 32 MB EDO 60ns. Bohužel moduly v MemTestu i GoldMemory vykazovaly chyby, ale chovalo se to kapánek podivně. V desce Asus P/I-P65UP5, pokud byly osazeny oba moduly, tak se chyby vyskytovaly, ale když jsem jeden modul vyměnil za jiný dobrý 32MB kus, tak se chyba neobjevila ani u jednoho Kingstonu. V desce Asus P6NP5 se však chyby objevovaly i s jedním Kingstonem a druhým OK modulem, takže jsem zjistil, který modul je vadný. Podle hodnot z MemTestu jsem pak usoudil, že chybuje pouze bit č. 1 a 3, což při použitých 4-bitových paměťových čipech znamená, že vadný bude asi jen jeden z 16.

1. průchod - 1 chyba na adrese 00661310 - 1 bit (bit č. 3) 2. průchod - 2 chyba na adrese 01905830 - 1 bit (bit č. 1) 3. průchod - 2 chyba na adrese 00662310 - 1 bit (bit č. 3) 4. průchod - 1 chyba na adrese 00661310 - 1 bit (bit č. 3) |

Mapování bylo naštěstí přímočaré, takže bity 0 - 3 v MemTestu odpovídaly bitům 0 - 3 na SIMM a z toho jsem se multimetrem dopískal, že spoje vedou ke krajnímu čipu C9. Naštěstí jsem měl v šuplíku jeden náhradní čip MN4117405CSJ-06 od Panasonicu se stejnou organizací (též EDO 60 ns). Napřed jsem zkusil původní čip Vanguard VG2617405DJ-6 jen pofoukat horkovzduchem, ale to nemělo žádný efekt, takže jsem ho vyměnil a modul funguje (testováno několik hodin v MemTestu bez chyb).

|

Jak předělat registered SDRAM na běžný SDRAM DIMM

3.4.2024 Na VOGONS fóru jsem našel zajímavé vlákno: jak předělat registered SDRAM na běžný SDRAM DIMM. Kdysi se totiž daly vyřazené registered SDRAMky větších kapacit ze serverů koupit mnohem levněji než obyčejné, protože v běžných desktopových deskách nefungovaly a tak byly pro naprostou většinu BFU nepoužitelné. Uživatel Snufkin vykoumal, že na registered SDRAMkách je navíc na datových linkách nějaký latch s 3-stavovým výstupem typu SN74ALVC16835, jehož vstup LE (Latch Enable) se ovládá přes invertor pinem 147 REGE (REGister Enable), který nemají běžné desktopové desky v DIMM slotu zapojený. Když je na REGE úroveň log. 0, funguje paměť v průchozím (buffered) režimu a když je na REGE úroveň log. 1, funguje v registered režimu (při náběžné hraně hodin latchne a drží data). Na pinu REGE je na modulu běžně zapojen pull-up odpor, takže pokud je na MB nezapojený, je aktivní registered režim. Stačí tedy invertor odpájet a propojit plošky jeho vstupu a výstupu drátkem nebo jednoduše drátkem přizemnit vstup invertoru.9.4.2024 Prohrábnul jsem své zásoby starých SDRAM DIMMů a našel 2 veliké ECC registered moduly IBM MT18LSDT6472G-133B1. Ty jsou osazené 18 paměťovými čipy Micron MT48LC64M4A2-75, 3 registry 74ALVCF162835APA a PLL PI6C2510-133L. Odpočítal jsem pin 147 (REGE) a zjistil, že vede na vstup 5-pinového SMD invertoru a je tažený pull-up odporem na VCC. Provedl jsem tedy nejjednodušší mod přidáním cínové kapky přímo na vstupní pin invertoru mezi sousední pin GND. Paměti jsem strčil do testovací desky Gigabyte GA-5AA a deska naběhla s krásným 1 GB RAM, o tom jsme si mohli v té době nechat jen zdát. Paměti jsem projel testem GoldMemory a prošly bez chyb.

|

|

|

| reg. SDRAM DIMM 512MB-top | reg. SDRAM DIMM 512MB-bottom | unreg. mod-blob |